# Corel2C v6.0

Handbook

© 2009 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200090-5

Release: November 2009

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel, IGLOO, Actel Fusion, ProASIC, Libero, Pigeon Point and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

|   | Introduction5Core Overview5Core Version5Supported Interfaces5Utilization and Performance6Configuration Example9                                                                                                      |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Design Description11I/O Signals11Verilog/VHDL Parameters12Serial and APB Interfaces14Functional Block Descriptions15Operation Details17Register Map and Descriptions19                                               |

| 2 | Tool Flows39SmartDesign39Simulation Flows41Synthesis in Libero IDE:41Place-and-Route in Libero IDE41                                                                                                                 |

| 3 | Example Application and Hints43Software Driver43Usage with Cortex-M143Hints on I/O Pad Requirements43Hints on Configuring WIRED-AND Bidirectional Buffers in RTL44Hints on Meeting SMBus/PMBus Timing Requirements44 |

| 4 | List of Document Changes                                                                                                                                                                                             |

| A | Product Support47Customer Service47Actel Customer Technical Support Center47Actel Technical Support47Website47Contacting the Customer Technical Support Center47Index49                                              |

# Introduction

## **Core Overview**

#### **Intended Use**

Corel2C provides an APB-driven serial interface, supporting I<sup>2</sup>C, SMBus, and PMBus data transfers. Several Verilog/VHDL parameters are available to minimize FPGA fabric area for a given application. Corel2C also allows for multiple I<sup>2</sup>C channels, reusing logic across channels to reduce overall tile count.

#### **Key Features**

- Conforms to the Philips Inter-Integrated Circuit (I<sup>2</sup>C) v2.1 Specification (7-bit addressing format at 100 Kbps and 400 Kbps data rates)

- Supports SMBus v2.0 Specification

- Supports PMBus v1.1 Specification

- Data transfers up to at least 400 kbps nominally; faster rates can be achieved depending on external load and/or I/O pad circuitry

- Modes of operation configurable to minimize size

- Advanced Peripheral Bus (APB) register interface

- Multi-master collision detection and arbitration

- Own address and general call address detection

- Second Slave address decode capability

- Data transfer in multiples of bytes

- SMBus timeout and real-time idle condition counters

- IPMI 3 ms SCL low timeout

- Optional SMBus signals, SMBSUS\_N and SMBALERT\_N, controllable via APB IF

- Configurable spike suppression width

- Multiple channel configuration option

# **Core Version**

This handbook supports CoreI2C version 6.0.

# **Supported Interfaces**

CoreI2C is available with the following interfaces:

- Serial I<sup>2</sup>C/SMBus/PMBus Interface

- APB Interface for register access

These interfaces are further described in the "Serial and APB Interfaces" section on page 14.

# **Utilization and Performance**

CoreI2C has been implemented in several of Actel's device families using standard speed grades. A summary of various implementation data is listed in Table 1 through Table 5 on page 8.

| Table 1 • | Corel2C Device Utilization and Performance (Slave-only I <sup>2</sup> | <sup>2</sup> C configuration) |

|-----------|-----------------------------------------------------------------------|-------------------------------|

|-----------|-----------------------------------------------------------------------|-------------------------------|

|                          |            | Tiles         |       | Utilizati | Performance |     |

|--------------------------|------------|---------------|-------|-----------|-------------|-----|

| Family                   | Sequential | Combinatorial | Total | Device    | Total %     | MHz |

| Fusion                   | 51         | 310           | 361   | AFS600    | 2.6         | 130 |

| IGLOO <sup>®</sup> /e    | 51         | 310           | 361   | AGLE600V2 | 2.6         | 54  |

| ProASIC <sup>®</sup> 3/E | 51         | 310           | 361   | M1A3P250  | 5.9         | 127 |

| ProASIC <sup>PLUS®</sup> | 58         | 355           | 413   | APA075    | 13          | 68  |

| Axcelerator <sup>®</sup> | 58         | 199           | 257   | AX250     | 6.1         | 135 |

| RTAX-S                   | 58         | 299           | 257   | RTAX250S  | 6.1         | 101 |

Note: Data in this table were achieved using the Verilog RTL with typical synthesis and layout settings. Top-level parameters/generics were set as follows: I2C\_NUM=1, OPERATING\_MODE = 1, BAUD\_RATE\_FIXED = 1, BAUD\_RATE\_VALUE = 6, BCLK\_ENABLED = 0, GLITCHREG\_NUM = 3, SMB\_EN = 0, IPMI\_EN = 0, FREQUENCY = 0, FIXED\_SLAVE0\_ADDR\_EN = 1, FIXED\_SLAVE0\_ADDR\_VALUE = 0x20, ADD\_SLAVE1\_ADDRESS\_EN = 0, FIXED\_SLAVE1\_ADDR\_EN = 0, FIXED\_SLAVE1\_ADDR\_EN = 0.

| <i>Table 2</i> • Corel2C Device Utilization and Performance (Master/Slave I <sup>2</sup> C configuration) |

|-----------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------|

|                         |            | Tiles         |       | Utilizatio | Performance |     |

|-------------------------|------------|---------------|-------|------------|-------------|-----|

| Family                  | Sequential | Combinatorial | Total | Device     | Total %     | MHz |

| Fusion                  | 73         | 451           | 524   | AFS600     | 3.8         | 116 |

| IGLOO/e                 | 73         | 451           | 524   | AGLE600V2  | 3.8         | 52  |

| ProASIC3/E              | 73         | 451           | 524   | M1A3P250   | 8.5         | 125 |

| ProASIC <sup>PLUS</sup> | 81         | 499           | 580   | APA075     | 18.9        | 69  |

| Axcelerator             | 82         | 303           | 385   | AX250      | 9.1         | 135 |

| RTAX-S                  | 82         | 303           | 385   | RTAX250S   | 9.1         | 100 |

Note: Data in this table were achieved using the Verilog RTL with typical synthesis and layout settings. Top-level parameters/generics were set as follows: I2C\_NUM=1, OPERATING\_MODE = 0, BAUD\_RATE\_FIXED = 1, BAUD\_RATE\_VALUE = 6, BCLK\_ENABLED = 0, GLITCHREG\_NUM = 3, SMB\_EN = 0, IPMI\_EN = 0, FREQUENCY = 0, FIXED\_SLAVE0\_ADDR\_EN = 1, FIXED\_SLAVE0\_ADDR\_VALUE = 0x20, ADD\_SLAVE1\_ADDRESS\_EN = 0, FIXED\_SLAVE1\_ADDR\_EN = 0, FIXED\_SLAVE1\_ADDR\_VALUE = 0.

|                         | Tiles      |               |       |           | Utilization |                    |  |

|-------------------------|------------|---------------|-------|-----------|-------------|--------------------|--|

| Family                  | Sequential | Combinatorial | Total | Device    | Total %     | Performance<br>MHz |  |

| Fusion                  | 92         | 492           | 584   | AFS600    | 4.2         | 121                |  |

| IGLOO/e                 | 92         | 492           | 584   | AGLE600V2 | 4.2         | 52                 |  |

| ProASIC3/E              | 92         | 492           | 584   | M1A3P250  | 9.5         | 118                |  |

| ProASIC <sup>PLUS</sup> | 96         | 556           | 652   | APA075    | 21          | 65                 |  |

| Axcelerator             | 101        | 325           | 426   | AX250     | 10          | 111                |  |

| RTAX-S                  | 101        | 325           | 426   | RTAX250S  | 10          | 86                 |  |

#### Table 3 • CoreI2C Device Utilization and Performance (IPMI Master-TX/Slave-RX I<sup>2</sup>C configuration)

Note: Data in this table were achieved using the Verilog RTL with typical synthesis and layout settings. Top-level parameters/generics were set as follows: I2C\_NUM=1, OPERATING\_MODE = 2, BAUD\_RATE\_FIXED = 1, BAUD\_RATE\_VALUE = 6, BCLK\_ENABLED = 0, GLITCHREG\_NUM = 3, SMB\_EN=0, IPMI\_EN = 1, FREQUENCY = 30, FIXED\_SLAVE0\_ADDR\_EN = 1, FIXED\_SLAVE0\_ADDR\_VALUE = 0x20, ADD\_SLAVE1\_ADDRESS\_EN = 1, FIXED\_SLAVE1\_ADDR\_EN = 1, FIXED\_SLAVE1\_ADDR\_EN = 1, FIXED\_SLAVE1\_ADDR\_EN = 1, FIXED\_SLAVE1\_ADDR\_EN = 1, FIXED\_SLAVE1\_ADDR\_VALUE = 0x33.

|                         |            | Tiles         |       | Utilization |         | Performance |

|-------------------------|------------|---------------|-------|-------------|---------|-------------|

| Family                  | Sequential | Combinatorial | Total | Device      | Total % | MHz         |

| Fusion                  | 117        | 587           | 704   | AF\$600     | 5.1     | 112         |

| IGLOO/e                 | 117        | 587           | 704   | AGLE600V2   | 5.1     | 46          |

| ProASIC3/E              | 117        | 587           | 704   | M1A3P250    | 11.5    | 111         |

| ProASIC <sup>PLUS</sup> | 125        | 673           | 798   | APA075      | 26      | 54          |

| Axcelerator             | 127        | 400           | 527   | AX250       | 12      | 109         |

| RTAX-S                  | 127        | 400           | 527   | RTAX250S    | 12      | 80          |

Note: Data in this table were achieved using the Verilog RTL with typical synthesis and layout settings. Top-level parameters/generics were set as follows: I2C\_NUM=1, OPERATING\_MODE = 0, BAUD\_RATE\_FIXED = 1, BAUD\_RATE\_VALUE = 6, BCLK\_ENABLED = 0, GLITCHREG\_NUM = 3, SMB\_EN = 1, IPMI\_EN = 0, FREQUENCY = 30, FIXED\_SLAVE0\_ADDR\_EN = 1, FIXED\_SLAVE0\_ADDR\_VALUE = 0x20, ADD\_SLAVE1\_ADDRESS\_EN = 0, FIXED\_SLAVE1\_ADDR\_EN = 0, FIXED\_SLAVE1\_ADDR\_EN = 0.

|                         | Tiles      |               |       | Utilization |         | Performance |

|-------------------------|------------|---------------|-------|-------------|---------|-------------|

| Family                  | Sequential | Combinatorial | Total | Device      | Total % | MHz         |

| Fusion                  | 989        | 6,001         | 6,990 | AFS600      | 51      | 97          |

| IGLOO/e                 | 989        | 6,001         | 6,990 | AGLE600V2   | 51      | 44          |

| ProASIC3/E              | 989        | 6,001         | 6,990 | M1A3P600    | 51      | 105         |

| ProASIC <sup>PLUS</sup> | 1,099      | 6,887         | 7,986 | APA600      | 37      | 47          |

| Axcelerator             | 1,166      | 4,082         | 5,248 | AX1000      | 29      | 69          |

| RTAX-S                  | 1,166      | 4,082         | 5,248 | RTAX1000    | 29      | 64          |

| Table 5 • | Corel2C Device | Utilization | and Performance | (13 Channel IPM | I configuration) |

|-----------|----------------|-------------|-----------------|-----------------|------------------|

| Tubic 5   |                | ounzation   |                 |                 | rconnigaration   |

Note: Data in this table were achieved using the Verilog RTL with typical synthesis and layout settings. Top-level parameters/generics were set as follows: I2C\_NUM=13, OPERATING\_MODE=2, BAUD\_RATE\_FIXED=1, BAUD\_RATE\_VALUE=7, BCLK\_ENABLED=1, GLITCHREG\_NUM=3, SMB\_EN=0, IPMI\_EN=1, FREQUENCY=30, FIXED\_SLAVE0\_ADDR\_EN=0, FIXED\_SLAVE0\_ADDR\_VALUE=32, ADD\_SLAVE1\_ADDRESS\_EN=1, FIXED\_SLAVE1\_ADDR\_EN=1, and FIXED\_SLAVE1\_ADDR\_VALUE=20.

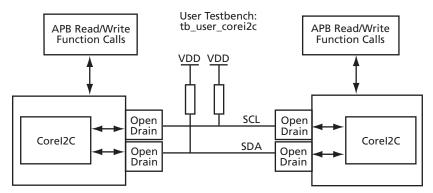

# **Configuration Example**

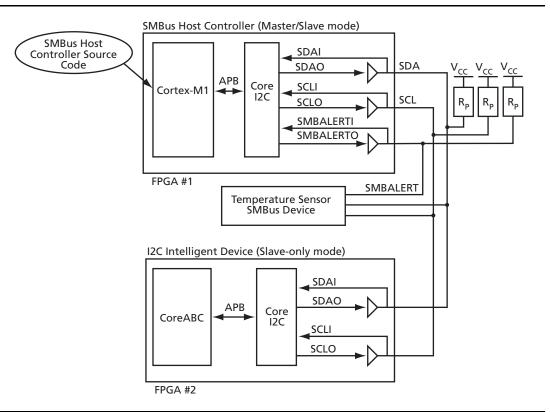

Figure 1 illustrates a typical application. Cortex<sup>TM</sup>-M1, coupled with Corel2C, masters communication with a SMBus Temperature Sensor slave, and an  $I^2C$  slave in FPGA #2. In FPGA #2, Corel2C is configured in Slave-only mode with CoreABC as its control.

Figure 1 • CoreI2C SMBus Application Example

# 1 – Design Description

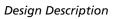

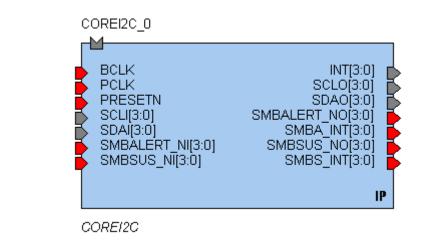

# I/O Signals

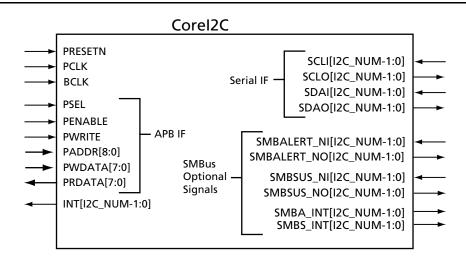

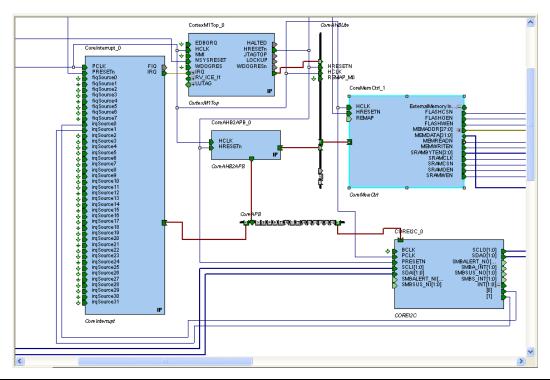

The port signals for the CoreI2C macro are illustrated in Figure 1-1 and defined in Table 1-1.

Figure 1-1 • Corel2C I/O Signal Diagram

| Name                  | Туре   | Description                                                                                                                                                                    |  |  |

|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| APB Interface         |        |                                                                                                                                                                                |  |  |

| PCLK                  | Input  | APB System Clock; Reference clock for all internal logic                                                                                                                       |  |  |

| PRESETN               | Input  | APB active low asynchronous reset                                                                                                                                              |  |  |

| PADDR[8:0]            | Input  | APB address bus; address internal registers. Bits 8 to 5 function as address pointers to one of the 16 channels.                                                               |  |  |

| PSEL                  | Input  | APB Slave Select; select signal for register for reads or writes                                                                                                               |  |  |

| PENABLE               | Input  | APB Strobe. This signal indicates the second cycle of an APB transfer.                                                                                                         |  |  |

| PWRITE                | Input  | APB Write/Read. If high, a write occurs when an APB transfer takes place. If low, a read takes place.                                                                          |  |  |

| PWDATA[7:0]           | Input  | APB write data                                                                                                                                                                 |  |  |

| PRDATA[7:0]           | Output | APB read data                                                                                                                                                                  |  |  |

| INT[I2C_NUM-1:0]      | Output | Interrupt output; monitors status register.                                                                                                                                    |  |  |

| SMBA_INT[I2C_NUM-1:0] | Output | It Optional (if SMBus Enabled) interrupt output; monitors assertion of<br>SMBALERT_NI. Level sensitive; hence only the deassertion of<br>SMBALERT_NI will clear the interrupt. |  |  |

|                       |        | SMBSUS_NI. Level sensitive; hence only the deassertion of                                                                                                                      |  |  |

Note: All signals are active high (logic 1) unless otherwise noted.

| Table 1-1 • | Corel2C I/O Signal Descript | ions (continued) |

|-------------|-----------------------------|------------------|

|-------------|-----------------------------|------------------|

| Serial Interface         |        |                                                                                                                                   |

|--------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| SCLI[I2C_NUM-1:0]        | Input  | Wired-AND serial clock input                                                                                                      |

| SCLO[I2C_NUM-1:0]        | Output | Wired-AND serial clock output                                                                                                     |

| SDAI[I2C_NUM-1:0]        | Input  | Wired-AND serial data input                                                                                                       |

| SDAO[I2C_NUM-1:0]        | Output | Wired-AND serial data output                                                                                                      |

| SMBus Optional Signals   |        |                                                                                                                                   |

| SMBALERT_NI[I2C_NUM-1:0] | Input  | Wired-AND interrupt signal input; used in Master/Host mode to monitor if slave/devices want to force communication with the host. |

| SMBALERT_NO[I2C_NUM-1:0] | Output | Wired-AND interrupt signal input; used in Slave/device mode if the core wants to force communication with a host.                 |

| SMBSUS_NI[I2C_NUM-1:0]   | Input  | Suspend Mode signal input; used if core is Slave/device.<br>Not a Wired-AND signal.                                               |

| SMBSUS_NO[I2C_NUM-1:0]   | Output | Suspend Mode signal output; used if core is the Master/host.<br>Not a Wired-AND signal.                                           |

| Other Signals            | -      |                                                                                                                                   |

| BCLK                     | Input  | Pulse for SCL speed control. Used only if the configuration bits cr[2:0] = 111; otherwise, various divisions of PCLK are used.    |

Note: All signals are active high (logic 1) unless otherwise noted.

# **Verilog/VHDL Parameters**

CoreI2C has parameters (Verilog) or generics (VHDL) for configuring the RTL code, described in Table 1-2. All parameters and generics are integer types.

| Parameter Name  | Valid Range | Description                                                                                                                                                                                                                                              | Default |

|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| I2C_NUM         | 1 to 16     | Number of I <sup>2</sup> C channels                                                                                                                                                                                                                      | 1       |

| FREQUENCY       | 1 to 255    | PCLK frequency value in MHz. FREQUENCY parameter<br>is only necessary to configure optional SMBus or IPMI<br>timeout counters.                                                                                                                           |         |

| OPERATING_MODE  | 0 to 3      | 0: Full Master/Slave Tx/Rx modes.<br>1: Slave Tx/RX modes only.<br>2: Master Tx and Slave Rx modes only.<br>3: Slave Rx mode only.                                                                                                                       | 0       |

| BCLK_ENABLED    | 0 or 1      | 0: BCLK input is disabled, reducing tile count.<br>1: BCLK input is enabled.                                                                                                                                                                             | 1       |

| BAUD_RATE_FIXED | 0 or 1      | <ul> <li>0: Baud rate value (bits cr[2:0] in the Control Register) modified by an APB-accessible register.</li> <li>1: Baud rate value [bits cr[2:0] in the Control Register) is fixed to the parameter BAUD_RATE VALUE, reducing tile count.</li> </ul> | 0       |

Table 1-2 • Corel2C Parameters/Generics Descriptions

| BAUD_RATE_VALUE         | 0 to 7       | Fixed Baud Ra                                                                             | ate Values                                                                                                                                 |   |

|-------------------------|--------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---|

|                         |              | Bit Value:                                                                                | SCL Frequency:                                                                                                                             |   |

|                         |              | 000                                                                                       | PCLK frequency/256                                                                                                                         |   |

|                         |              | 001                                                                                       | PCLK frequency/224                                                                                                                         |   |

|                         |              | 010                                                                                       | PCLK frequency/192                                                                                                                         | 0 |

|                         |              | 011                                                                                       | PCLK frequency/160                                                                                                                         | 0 |

|                         |              | 100                                                                                       | PCLK frequency/960                                                                                                                         |   |

|                         |              | 101                                                                                       | PCLK frequency/120                                                                                                                         |   |

|                         |              | 110                                                                                       | PCLK frequency/60                                                                                                                          |   |

|                         |              | 111                                                                                       | BCLK frequency/8                                                                                                                           |   |

| SMB_EN                  | 0 or 1       |                                                                                           | he SMBus logic: SMBus register, real-time neout values.                                                                                    | 0 |

|                         |              | 0: SMBus logic not generated.                                                             |                                                                                                                                            |   |

| IPMI_EN                 | 0 or 1       | 1: Generates 3 ms SCL Low IPMI Required Timeo<br>Counter with error status and interrupt. |                                                                                                                                            |   |

|                         |              | 0: IPMI Timeout Counter not generated.                                                    |                                                                                                                                            |   |

| GLITCHREG_NUM           | 3 to 15      | to meet I <sup>2</sup> C fa<br>Mbps). 50 ns<br>PCLK frequer                               | egisters in the Glitch Filter. Correct value<br>ist mode (400 kbps) and fast mode plus (1<br>s spike suppression will depend on the<br>cy. | 3 |

|                         |              | Guideline:                                                                                |                                                                                                                                            |   |

|                         |              | PCLK Freq (M                                                                              | Hz) GlitchReg_Num for 50 ns<br>or Less Spike Suppression                                                                                   |   |

|                         |              | Freq ≤ 60                                                                                 | 3                                                                                                                                          |   |

|                         |              | 60 < Freq ≤ 80                                                                            | ) 4                                                                                                                                        |   |

|                         |              | 80 < Freq ≤ 10                                                                            | 00 5                                                                                                                                       |   |

|                         |              | 100 < Freq ≤ <sup>•</sup>                                                                 | 20 6                                                                                                                                       |   |

|                         |              | 120 < Freq ≤ <sup>2</sup>                                                                 | 40 7                                                                                                                                       |   |

|                         |              | 140 < Freq ≤ <sup>2</sup>                                                                 | 60 8                                                                                                                                       |   |

|                         |              | 160 < Freq ≤ <sup>2</sup>                                                                 | 80 9                                                                                                                                       |   |

|                         |              | 180 < Freq ≤ 2                                                                            | 200 10                                                                                                                                     |   |

| FIXED_SLAVE0_ADDR_EN    | 0 or 1       | 0: SLAVE0 add                                                                             | dress has APB write access.                                                                                                                | 0 |

|                         |              | 1: SLAVE0 ad                                                                              | dress is hardcoded, reducing tile count.                                                                                                   |   |

| FIXED_SLAVE0_ADDR_VALUE | 0x00 to 0x7F | Hardcoded SI                                                                              | AVE0 address value.                                                                                                                        | 0 |

| ADD_SLAVE1_ADDRESS_EN   | 0 or 1       | 0: SLAVE1 ad                                                                              | dress is not enabled.                                                                                                                      | 0 |

|                         |              |                                                                                           | dress is enabled.                                                                                                                          |   |

| FIXED_SLAVE1_ADDR_EN    | 0 or 1       | 0: SLAVE1 add                                                                             | dress has APB write access.                                                                                                                | 0 |

|                         |              |                                                                                           |                                                                                                                                            | - |

|                         |              | 1: SLAVET ad                                                                              | dress is hardcoded, reducing tile count.                                                                                                   |   |

#### Table 1-2 • Corel2C Parameters/Generics Descriptions (continued)

# **Serial and APB Interfaces**

## **Serial Interface**

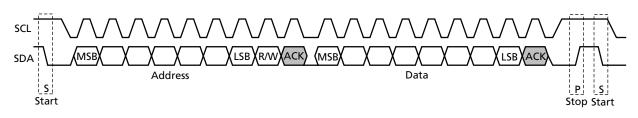

A typical I<sup>2</sup>C/IPMI/SMBus/PMBus 8-bit data transfer cycle is shown in Figure 1-2. A Master start condition is signalled by the SDA line going low while the SCL line is high. After a start condition, the master sends a slave address along with a read or write bit. The addressed slave acknowledges its address with an ACK, and then multiple bytes can be transferred with an ACK/NACK for each byte. Eventually the Master asserts a stop condition, which occurs when the SDA line goes high while the SCL line is high.

#### Figure 1-2 • Serial Interface Byte Transfer

A user of Corel2C must configure the system (logic, I/O pads, external circuitry and pull-up resistors) to ensure that the serial interface timings adhere to a given I<sup>2</sup>C/SMBus/PMBus specification.

Note: To adhere to additional SMBus/PMBus Hold times and Minimum Clock High Times, configure PCLK to be within the 5 Mhz to 20 Mhz range. Additionally, choose a Baud Rate Value so that the serial SCL clock will transfer data at or near the maximum frequency of 100 KHz (FSMB-max) to ensure that other potential clock stretching devices on the bus will not slow the clock frequency to below the minimum allowed SMBus clock of 10 KHz (FSMB-min).

For detailed timing information, refer to the I<sup>2</sup>C/IPMI/SMBus/PMBus Specifications directly.

### **APB Interface**

Figure 1-3 and Figure 1-4 depict typical write cycle and read cycle timing relationships relative to the system clock.

| PCLK        |                    |

|-------------|--------------------|

| PSEL        |                    |

| PWRITE      |                    |

| PENABLE     |                    |

| PADDR[8:0]  | Register Address X |

| PWDATA[7:0] | X Register Data X  |

#### Figure 1-3 • Data Write Cycle

| PCLK       |                  |

|------------|------------------|

| PSEL       |                  |

| PWRITE     |                  |

| PENABLE    |                  |

| FENADLE    |                  |

| PADDR[8:0] | Register Address |

# **Functional Block Descriptions**

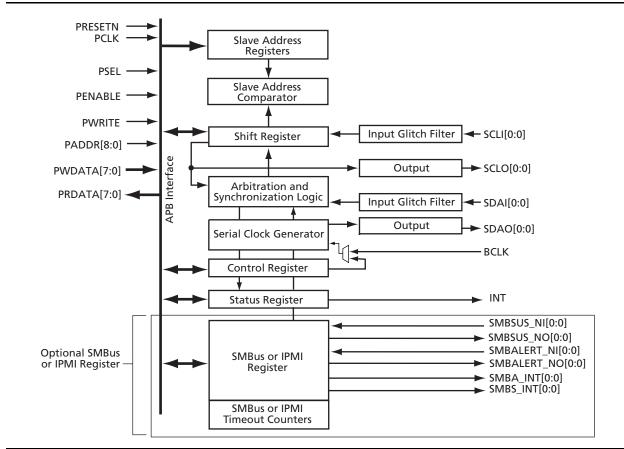

Corel2C, as shown in Figure 1-5, consists of APB interface registers, serial input spike filters, arbitration and synchronization logic, and a serial clock generation block. The following sections briefly describe each design block.

Figure 1-5 • Corel2C Block Diagram (single channel)

### **APB Interface**

Corel2C supports the Advanced Peripheral Bus (APB) interface, compatible with the Actel Core8051s and Cortex-M1 processor cores, as well as the CoreABC generic APB-based state machine controller.

The APB registers are defined and usage detailed in the "Register Map and Descriptions" section on page 1-19.

### **Input Glitch/Spike Filters**

Input signals are synchronized with the internal clock, PCLK. Spikes shorter than the parameterizeable glitch register length are filtered out.

## **Arbitration and Synchronization Logic**

In Master mode, the arbitration logic checks that every transmitted logic '1' actually appears as a logic '1' on the bus. If another device on the bus overrules a logic '1' and pulls the data line low, arbitration is lost and Corel2C immediately changes from Master transmitter to Slave receiver. The

synchronization logic synchronizes the serial clock generator block with the transmitted clock pulses coming from another master device.

The arbitration and synchronization logic also utilizes timeout requirements set forth in the SMBus Specification Version 2.0, or creates a 3 ms IPMI SCL Low Timeout.

#### **Serial Clock Generator**

This programmable clock pulse generator provides the serial bus clock pulses when Corel2C is in Master mode. The clock generator is switched off when Corel2C is in Save mode. The baud rate clock (BCLK) is a pulse-for-transmission speed control signal and is internally synchronized with the clock input. BCLK may be used to set the serial clock frequency when the cr[2:0] bits in the Control Register are set to 111; otherwise, PCLK divisions are used to determine the serial clock frequency. The actual non-stretched serial bus clock frequency can be calculated based on the setting in the cr2-0 fields of the Control Register and the frequencies of PCLK and BCLK. Refer to Table 1-5 on page 1-20 for configuration.

#### **Address Comparator**

The comparator checks the received seven-bit slave address with its own slave address, and optionally its own second address, slave1 (for dual-address applications). The comparator also compares the first received eight-bit byte with the general call address (00H). If a match is found, the Status Register is updated and an interrupt is requested.

## **Optional SMBus/IPMI Logic**

The optional SMBus / IPMI logic includes the SMBus signals, clock-low timeout counters, and reset logic; or when in IPMI mode, the optional 3 ms clock-low timeout counters (an SMBus clock low master reset example is demonstrated in the "Operation Details" section on page 1-17). SMBus/IPMI logic includes a top-level prescale counter, which counts in increments of 215 microseconds. A second smaller counter in each channel increments based on the prescale count of 215 microseconds. This design was chosen to reduce overall area at the expense of timeout precision (when the clock-low condition occurs in IPMI mode, the free running 215 microsecond counter may be anywhere in its count). As such, the 3 ms timeout flag will occur between 3.010 and 3.225 ms. The 35 ms SMBus master-holding-clock-low flag will occur between 35.045 and 35.260 ms, and the 25 ms SMBus timeout flag will occur between 25.155 and 25.370 ms.

# **Operation Details**

## I<sup>2</sup>C Operating Modes

Corel2C logic can operate in the following four modes:

1. Master Transmitter Mode:

Serial data output through SDA while SCL outputs the serial clock.

- Master Receiver Mode: Serial data is received via SDA while SCL outputs the serial clock.

- 3. Slave Receiver Mode:

Serial data and the serial clock are received through SDA and SCL.

4. Slave Transmitter Mode:

Serial data is transmitted via SDA while the serial clock is input through SCL.

## Slave Mode Example

After setting the ens1 bit in the Control Register, the core is in the not addressed Slave mode. In Slave mode, the core looks for its own slave address and the general call address. If one of these addresses is detected, the core switches to addressed Slave mode and generates an interrupt request. Then the core can operate as a Slave transmitter or a Slave receiver.

Transfer example:

- Microcontroller sets ens1 and aa bits

- Core receives own address and 0.

- Core generates interrupt request; Status Register = 0x60 (Table 1-11 on page 1-26)

- Microcontroller prepares for receiving data and then clears si bit.

- Core receives next data byte and then generates interrupt request. The Status Register contains 0x80 or 0x88 value depending on aa bit (Table 1-11 on page 1-26).

- Transfer is continued according to Table 1-11 on page 1-26.

### Master Mode Example

When the microcontroller wishes to become the bus master, the core waits until the serial bus is free. When the serial bus is free, the core generates a start condition, sends the slave address and transfers the direction bit. The core can operate as a Master transmitter or as a Master receiver, depending on the transfer direction bit.

Transfer example:

- Microcontroller sets ens1 and sta bits.

- Core sends START condition and then generates interrupt request; Status Register = 0x08 (Table 1-9 on page 1-21).

- Microcontroller writes the Data Register (7-bit slave address and 0) and then clears si bit.

- Core sends Data Register contents and then generates interrupt request. The Status Register contains 0x18 or 0x20 value, depending on received ACK bit (Table 1-9 on page 1-21).

- Transfer is continued according to Table 1-9 on page 1-21.

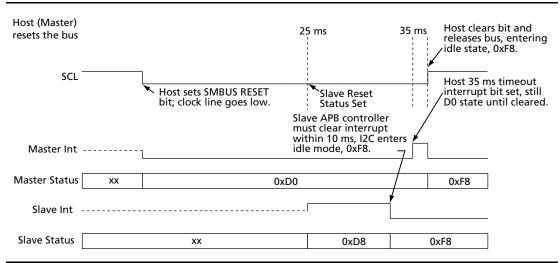

### **SMBus Clock Low Reset Example**

If the clock line is held low by a Master who has initiated a bus reset with the SMBus register, the following sequence should occur. Refer to Figure 1-6.

- Transfer example:

- The Master device sets SMBUS RESET bit, forcing the clock line low; the master device enters the resetting state, 0xD0, and an interrupt is generated after 35 ms.

- A Slave device will enter the reset state, 0xD8, after 25 ms and an interrupt will be generated. Once the interrupt is asserted, the APB controller of the slave device will need to clear the interrupt within 10 ms per the SMBus Specification v.2.0, and the Slave device will enter the idle state, 0xF8.

- After 35 ms, the Master device's interrupt will be asserted, and the APB controller of the master device will eventually clear the interrupt, forcing the Master device into the idle state, 0xF8.

Figure 1-6 • SMBus Bus Reset Sequence

# **Register Map and Descriptions**

PADDR[8:5] bits determine which I<sup>2</sup>C channel is being addressed, as shown in Table 1-3. Table 1-4 defines the register map and reset values of each channel's APB-accessible registers. 0x denotes hexadecimal, 0b denotes binary, and 0d denotes decimal format. "X" implies an unknown condition. "-"implies don't care condition. Type designations: R is read-only, R/W is read/write.

Table 1-3 • Corel2C Per Channel Pointer Addressing

| PADDR[8:5]       | Туре | Reset Value | Brief Description                                                                                                                                                                                                                                                                                                              |

|------------------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel ID Value | N/A  | N/A         | Bits 8 to 5 of PADDR function as address pointers to one of the 16 channels. Note that the Channel ID Value does not apply to the ADDR0 and ADDR1 registers shown in Table 1-4. The values in those registers are the same for all channels.         PADDR[8:5]       Channel Number         0000       0         0001       1 |

|                  |      |             | 1111 15                                                                                                                                                                                                                                                                                                                        |

| Table 1-4 • | <b>Corel2C Internal</b> | Register | Address Map  |

|-------------|-------------------------|----------|--------------|

|             | corcize internat        | Register | Address Midp |

| PADDR[4:0] | Register<br>Name | Туре | Width | Reset Value | Brief Description                                                                                                                                                                                                                                                                           |

|------------|------------------|------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00       | CTRL             | R/W  | 8     | 0x00        | Control Register; used to configure each I <sup>2</sup> C channel.                                                                                                                                                                                                                          |

| 0x04       | STAT             | R    | 8     | 0xF8        | Status Register; read-only value yields the current state of the particular I <sup>2</sup> C channel.                                                                                                                                                                                       |

| 0x08       | DATA             | R/W  | 8     | 0x00        | Data Register; I <sup>2</sup> C channel read/write data to/from the serial IF.                                                                                                                                                                                                              |

| 0x0C       | ADDR0            | R/W  | 8     | 0x00        | Slave0 Address Register; contains the programmable Slave0 address of all channels.                                                                                                                                                                                                          |

|            |                  |      |       |             | Note: The Slave0 Address Register is a single register<br>that is used in all channels. Only PADDR[4:0] are<br>required to write ADDR0; PADDR[8:5] are "don't<br>care" bits.                                                                                                                |

| 0x10       | SMB              | R/W  | 8     | 0b01X1X000  | SMBus or IPMI Register                                                                                                                                                                                                                                                                      |

|            |                  |      |       |             | SMBus Context: Configuration register for SMBus timeouts and reset condition and for the optional SMBus signals SMBALERT_N and SMBSUS_N.                                                                                                                                                    |

|            |                  |      |       |             | IPMI Context: Enable/Disable IPMI SCL low timeout                                                                                                                                                                                                                                           |

| 0x1C       | ADDR1            | R/W  | 8     | 0x00        | Slave1 Address Register; contains the programmable<br>Slave1 address of all channels. When this Slave1<br>address is enabled yet fixed, the register will have a<br>R/W bit to enable/disable Slave1 comparisons. Only the<br>enable/disable bit will be R/W. The address is write<br>only. |

|            |                  |      |       |             | Note: The Slave1 Address Register is a single register<br>that is used in all channels. Only the<br>enable/disable bit is R/W. Only PADDR[4:0] are<br>required to write ADDR0; PADDR[8:5] are "don't<br>care" bits.                                                                         |

The following sections and tables detail the APB-accessible registers within each Corel2C channel.

## **Control Register**

The Control Register is described in Table 1-5 and Table 1-6 on page 1-20. The CPU can read from and write to this 8-bit, directly addressable APB. Two bits are affected by the Corel2C: the si bit is set when a serial interrupt is requested and the sto bit is cleared when a STOP condition is present on the bus.

Table 1-5 • Control Register

| PADDR[4:0] | Register Name | Туре | Width | Reset Value | Description                                                        |

|------------|---------------|------|-------|-------------|--------------------------------------------------------------------|

| 0x00       | CTRL          | R/W  | 8     |             | Control Register; used to configure each I <sup>2</sup> C channel. |

| Bits | Name | Туре | Description |                                                                                                                                 |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

|------|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7    | cr2  | R/W  | Cloc        | k rat                                                                                                                           | e bit i | 2; refer to bit 0.                                                                                                                                                   |  |  |  |  |  |  |  |

| 6    | ens1 | R/W  |             |                                                                                                                                 |         | nen ens1 = 0, the sda and scl outputs are in a high impedance table and out signals are ignored. When ens1 = 1, the channel is enabled.                              |  |  |  |  |  |  |  |

| 5    | sta  | R/W  |             | ne START flag. When sta = 1, the channel checks the status of the serial bus and enerates a START condition if the bus is free. |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 4    | sto  | R/W  |             | The STOP flag. When sto = 1 and the channel is in a Master mode, a STOP condition is transmitted to the serial bus.             |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 3    | si   | R/W  | char        | nge ii                                                                                                                          | n the   | rrupt flag. The si flag is set by the channel whenever there is a serviceable<br>Status Register. After the register has been updated, the si" bit must be<br>tware. |  |  |  |  |  |  |  |

|      |      |      | The         | si bit                                                                                                                          | is dir  | ectly readable via the APB INTERRUPT signal.                                                                                                                         |  |  |  |  |  |  |  |

| 2    | aa   | R/W  | The         | Asse                                                                                                                            | rt Ack  | nowledge flag.                                                                                                                                                       |  |  |  |  |  |  |  |

|      |      |      | Whe         | en aa                                                                                                                           | = 1, a  | n acknowledge (ACK) will be returned when:                                                                                                                           |  |  |  |  |  |  |  |

|      |      |      | The         | "owi                                                                                                                            | n slav  | e address" has been received.                                                                                                                                        |  |  |  |  |  |  |  |

|      |      |      |             | •                                                                                                                               |         | Il address has been received while the gc bit in the Address register is set.                                                                                        |  |  |  |  |  |  |  |

|      |      |      |             | -                                                                                                                               |         | as been received while the channel is in the Master receiver mode.                                                                                                   |  |  |  |  |  |  |  |

|      |      |      |             | A data byte has been received while the channel is in the Slave receiver mode.                                                  |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

|      |      |      |             | When aa = 0, a not acknowledge (NACK) will be returned when:                                                                    |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

|      |      |      |             | A data byte has been received while the channel is in the Master receiver mode.                                                 |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

|      |      |      | A da        | ata by                                                                                                                          | /te ha  | as been received while the channel is in the Slave receiver mode.                                                                                                    |  |  |  |  |  |  |  |

| 1    | cr1  | R/W  | Seria       | Serial clock rate bit 1; refer to bit 0.                                                                                        |         |                                                                                                                                                                      |  |  |  |  |  |  |  |

| 0    | cr0  | R/W  | Seria       | al clo                                                                                                                          | ck rat  | te bit 0;                                                                                                                                                            |  |  |  |  |  |  |  |

|      |      |      | Cloc        | k Rat                                                                                                                           | e is d  | efined as follows:                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | cr2         | cr1                                                                                                                             | cr0     | SCL Frequency                                                                                                                                                        |  |  |  |  |  |  |  |

|      |      |      | 0           | 0                                                                                                                               | 0       | PCLK frequency/256                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 0           | 0                                                                                                                               | 1       | PCLK frequency/224                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 0           | 1                                                                                                                               | 0       | PCLK frequency/192                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 0           | 1                                                                                                                               | 1       | PCLK frequency/160                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 1           | 0                                                                                                                               | 0       | PCLK frequency/960                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 1           | 0                                                                                                                               | 1       | PCLK frequency/120                                                                                                                                                   |  |  |  |  |  |  |  |

|      |      |      | 1           | 1                                                                                                                               | 0       | PCLK frequency/60                                                                                                                                                    |  |  |  |  |  |  |  |

|      |      |      | 1           | 1                                                                                                                               | 1       | BCLK frequency/8                                                                                                                                                     |  |  |  |  |  |  |  |

Table 1-6 • Control Register Bit Fields

## **Status Register**

The Status Register is read-only. The status values are listed, depending on mode of operation, in Table 1-9 through Table 1-13 on page 1-32. Whenever there is a change of state, an INTERRUPT (INT) is asserted. After updating any registers, the APB interface control must clear the INTERRUPT (INT) by clearing the si bit of the Control Register.

Table 1-7 •Status Register

| PADDR[4:0] | Register Name | Туре | Width | Reset<br>Value | Description                                                                                 |

|------------|---------------|------|-------|----------------|---------------------------------------------------------------------------------------------|

| 0x04       | STAT          | R    | 8     |                | Status Register; read-only value yields the current state of each I <sup>2</sup> C channel. |

Table 1-8 •Status Register Bit Fields

| Bits | Name   | Туре | Field Description                                                                               |

|------|--------|------|-------------------------------------------------------------------------------------------------|

| 7:0  | Status | R    | Read-Only Status Code. Refer to Following Tables for Code Descriptions based on Operating Mode. |

Table 1-9throughTable 1-13onpage 1-32defineStatusRegisterCodeDescriptionsandsubsequentActionbased on the four possible operating modes.

| Status |                                                      | Data Register   | Cor | Control Register<br>Bits |    | ster |                                                                                           |

|--------|------------------------------------------------------|-----------------|-----|--------------------------|----|------|-------------------------------------------------------------------------------------------|

| Code   | Status                                               | Action          | sta | sto                      | si | aa   | Next Action Taken by I <sup>2</sup> C Channel                                             |

| 0x08   | A START condition<br>has been<br>transmitted.        | Load SLA + W    | -   | 0                        | 0  | _    | SLA + W will be transmitted; ACK will be received.                                        |

| 0x10   | A repeated START condition has been transmitted.     | Load SLA + W    | -   | 0                        | 0  | _    | SLA + W will be transmitted; ACK will be received.                                        |

|        |                                                      | or load SLA + R | -   | 0                        | 0  | -    | SLA + R will be transmitted; channel will be switched to MST/REC mode.                    |

| 0x18   | SLA + W has been transmitted; ACK has been received. | Load data byte  | 0   | 0                        | 0  | -    | Data byte will be transmitted; ACK will be received.                                      |

|        |                                                      | or no action    | 1   | 0                        | 0  | Ι    | Repeated START will be transmitted.                                                       |

|        |                                                      | or no action    | 0   | 1                        | 0  | _    | STOP condition will be transmitted; sto flag will be reset.                               |

|        |                                                      | or no action    | 1   | 1                        | 0  | _    | STOP condition followed by a START condition will be transmitted; sto flag will be reset. |

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

| Status |                                                                                   | Data Register  | Cor | ntrol I<br>Bi | -  | ster |                                                                                           |

|--------|-----------------------------------------------------------------------------------|----------------|-----|---------------|----|------|-------------------------------------------------------------------------------------------|

| Code   | Status                                                                            | Action         | sta | sto           | si | aa   | Next Action Taken by I <sup>2</sup> C Channel                                             |

| 0x20   | SLA + W has been<br>transmitted; NACK<br>has been received.                       | Load data byte | 0   | 0             | 0  | -    | Data byte will be transmitted; ACK will be received.                                      |

|        |                                                                                   | or no action   | 1   | 0             | 0  | -    | Repeated START will be transmitted.                                                       |

|        |                                                                                   | or no action   | 0   | 1             | 0  | I    | STOP condition will be transmitted; sto flag will be reset.                               |

|        |                                                                                   | or no action   | 1   | 1             | 0  | -    | STOP condition followed by a START condition will be transmitted; sto flag will be reset. |

| 0x28   | Data byte in Data<br>Register has been<br>transmitted; ACK has<br>been received.  | Load data byte | 0   | 0             | 0  | -    | Data byte will be transmitted; ACK bit will be received.                                  |

|        |                                                                                   | or no action   | 1   | 0             | 0  | I    | Repeated START will be transmitted.                                                       |

|        |                                                                                   | or no action   | 0   | 1             | 0  | 1    | STOP condition will be transmitted; sto flag will be reset.                               |

|        |                                                                                   | or no action   | 1   | 1             | 0  | -    | STOP condition followed by a START condition will be transmitted; sto flag will be reset. |

| 0x30   | Data byte in Data<br>Register has been<br>transmitted; NACK<br>has been received. | No action      | 1   | 0             | 0  | I    | Repeated START will be transmitted.                                                       |

|        |                                                                                   | or no action   | 0   | 1             | 0  | I    | STOP condition will be transmitted; sto flag will be reset.                               |

|        |                                                                                   | or no action   | 1   | 1             | 0  | -    | STOP condition followed by a START condition will be transmitted; sto flag will be reset. |

| 0x38   | Arbitration lost in<br>SLA + R/W or data<br>bytes.                                | No action      | 0   | 0             | 0  | I    | The bus will be released; not-addressed slave mode will be entered.                       |

|        |                                                                                   | or no action   | 1   | 0             | 0  | Ι    | A START condition will be transmitted when the bus becomes free.                          |

Table 1-9 • Status Register – Master Transmitter Mode (continued)

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

| Status | tus Data Register                                        |           | Cor | ntrol I<br>Bit | -  | ster |                                                                                                               |

|--------|----------------------------------------------------------|-----------|-----|----------------|----|------|---------------------------------------------------------------------------------------------------------------|

| Code   | Status                                                   | Action    | sta | sto            | si | aa   | Next Action Taken by I <sup>2</sup> C Channel                                                                 |

| 0xD0   | SMB_EN = 1:<br>SMBus Master Reset<br>has been activated. | No action | -   | -              | -  | Η    | Wait 35 ms for interrupt to be set, clear interrupt and proceed to 0xF8 state.<br>Only valid when SMB_EN = 1. |

| 0xD8   | IPMI_EN = 1:<br>3 ms SCL low time<br>has been reached.   | No action | _   | Ι              | 0  | Ι    | 3 ms SCL low time has been reached.<br>Only valid when IPMI_EN = 1.                                           |

Table 1-9 •

Status Register – Master Transmitter Mode (continued)

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

#### Table 1-10 • Status Register – Master Receiver Mode

| Status |                                                             | APB Config.          | Со  | ntrol<br>Bi | Regis<br>ts | ster |                                                                                           |

|--------|-------------------------------------------------------------|----------------------|-----|-------------|-------------|------|-------------------------------------------------------------------------------------------|

| Code   | Status                                                      | Register Action      | sta | sto         | si          | aa   | Next Action Taken by I <sup>2</sup> C Channel                                             |

| 0x08   | A START condition has been transmitted.                     | Load SLA + R         | -   | 0           | 0           | -    | SLA + R will be transmitted; ACK will be received.                                        |

| 0x10   | A repeated START condition has been transmitted.            | Load SLA + R         | Ι   | 0           | 0           | -    | SLA + R will be transmitted; ACK will be received.                                        |

|        |                                                             | or load SLA + W      | -   | 0           | 0           | -    | SLA + W will be transmitted; Corel2C will be switched to MST/TRX mode.                    |

| 0x38   | Arbitration lost.                                           | No action            | 0   | 0           | 0           | -    | The bus will be released; Corel2C will enter slave mode.                                  |

|        |                                                             | or no action         | 1   | 0           | 0           | -    | A start condition will be transmitted when the bus becomes free.                          |

| 0x40   | SLA + R has been<br>transmitted; ACK has<br>been received.  | No action            | 0   | 0           | 0           | 0    | Data byte will be received; NACK will be returned.                                        |

|        |                                                             | or no action         | 0   | 0           | 0           | 1    | Data byte will be received; ACK will be returned.                                         |

| 0x48   | SLA + R has been<br>transmitted; NACK has<br>been received. | No action            | 1   | 0           | 0           | -    | Repeated START condition will be transmitted.                                             |

|        |                                                             | or no action         | 0   | 1           | 0           | -    | STOP condition will be transmitted; sto flag will be reset.                               |

|        |                                                             | or no action         | 1   | 1           | 0           | -    | STOP condition followed by a START condition will be transmitted; sto flag will be reset. |

| 0x50   | Data byte has been<br>received; ACK has<br>been returned.   | Read data byte       | 0   | 0           | 0           | 0    | Data byte will be received; NACK will be returned.                                        |

|        |                                                             | or read data<br>byte | 0   | 0           | 0           | 1    | Data byte will be received; ACK will be returned.                                         |

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

| Status |                                                            | APB Config.          | Control Register<br>Bits |     |    |    |                                                                                                                  |

|--------|------------------------------------------------------------|----------------------|--------------------------|-----|----|----|------------------------------------------------------------------------------------------------------------------|

| Code   | Status                                                     | Register Action      | sta                      | sto | si | aa | Next Action Taken by I <sup>2</sup> C Channel                                                                    |

| 0x58   | Data byte has been<br>received; NACK has<br>been returned. | Read data byte       | 1                        | 0   | 0  | -  | Repeated START condition will be transmitted.                                                                    |

|        |                                                            | or read data<br>byte | 0                        | 1   | 0  | -  | STOP condition will be transmitted; sto flag will be reset.                                                      |

|        |                                                            | or read data<br>byte | 1                        | 1   | 0  | -  | STOP condition followed by a START condition will be transmitted; sto flag will be reset.                        |

| 0xD0   | SMB_EN = 1:<br>SMBus Master Reset<br>has been activated.   | No Action            | _                        | -   | 0  | -  | Wait 35 ms for interrupt to be set; clear<br>interrupt and proceed to 0xF8 state.<br>Only valid when SMB_EN = 1. |

| 0xD8   | IPMI_EN = 1:<br>3 ms SCL low time has<br>been reached.     | No action            | _                        | _   | 0  | _  | 3 ms SCL low time has been reached.<br>Only valid when IPMI_EN = 1.                                              |

#### Table 1-10 • Status Register – Master Receiver Mode (continued)

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

#### Table 1-11 • Status Register – Slave Receiver Mode

| Status |                                                                                                            | Data Register        | Co  | ntrol<br>Bi | -  | ter |                                                       |

|--------|------------------------------------------------------------------------------------------------------------|----------------------|-----|-------------|----|-----|-------------------------------------------------------|

| Code   | Status                                                                                                     | Action               | sta | sto         | si | aa  | Next Action Taken by I <sup>2</sup> C Channel         |

| 0x60   | Own SLA + W has<br>been received; ACK<br>has been returned.                                                | No action            | _   | 0           | 0  | 0   | Data byte will be received and NACK will be returned. |

|        |                                                                                                            | or no action         | -   | 0           | 0  | 1   | Data byte will be received and ACK will be returned.  |

| 0x68   | Arbitration lost in<br>SLA + R/W as master;<br>own SLA + W has<br>been received, ACK<br>returned.          | No action            | -   | 0           | 0  | 0   | Data byte will be received and NACK will be returned. |

|        |                                                                                                            | or no action         | -   | 0           | 0  | 1   | Data byte will be received and ACK will be returned.  |

| 0x70   | General call address<br>(00H) has been<br>received; ACK has<br>been returned.                              | No action            | -   | 0           | 0  | 0   | Data byte will be received and NACK will be returned. |

|        |                                                                                                            | or no action         | -   | 0           | 0  | 1   | Data byte will be received and ACK will be returned.  |

| 0x78   | Arbitration lost in<br>SLA + R/W as master;<br>general call address<br>has been received,<br>ACK returned. | No action            | -   | 0           | 0  | 0   | Data byte will be received and NACK will be returned. |

|        |                                                                                                            | or no action         | -   | 0           | 0  | 1   | Data byte will be received and ACK will be returned.  |

| 0x80   | Previously addressed<br>with own SLV<br>address; DATA has<br>been received; ACK<br>returned.               | Read data byte       | _   | 0           | 0  | 0   | Data byte will be received and NACK will be returned. |

|        |                                                                                                            | or read data<br>byte | _   | 0           | 0  | 1   | Data byte will be received and ACK will be returned.  |

- 1. SLA = slave address

- 2. SLV = slave

- 3. REC = receiver

- 4. TRX = transmitter

- 5. SLA + W = Master sends slave address, then writes data to slave.

- 6. SLA + R = Master sends slave address, then reads data from slave.

| Status |                                                                                                   | Data Register        | Co  | Control Register<br>Bits |    | ter |                                                                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------|----------------------|-----|--------------------------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code   | Status                                                                                            | Action               | sta | sto                      | si | aa  | Next Action Taken by I <sup>2</sup> C Channel                                                                                                                      |

| 0x88   | Previously addressed<br>with own SLA; DATA<br>byte has been<br>received; NACK<br>returned         | Read data byte       | 0   | 0                        | 0  | 0   | Switched to not-addressed SLV mode;<br>no recognition of own SLA or general<br>call address.                                                                       |